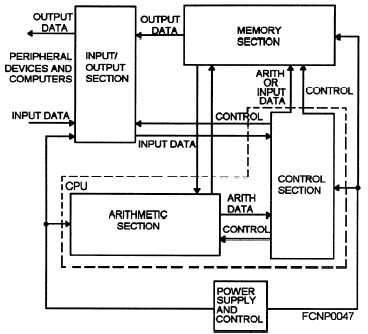

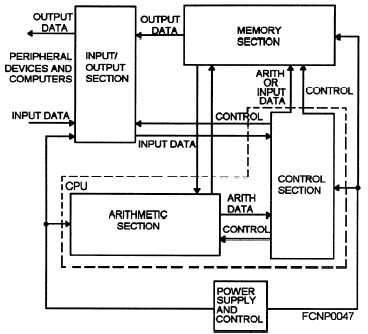

Figure 5-2.—Representative block diagram showing the relationship of the control section to the other functional areas of a

computer.

The control section consists of several basic

logically defined areas. These logically defined areas

work closely with each other. They are the basis for the

operations of the control section in most computers.

They include:

Timing

Instruction and control

Addressing

Interrupts

Control memory

Cache memory

Read-only memory (ROM)

TIMING

Timing in a computer regulates the flow of signals

that control the operation of the computer. Without

timing, events in a computer would not take place. The

computer’s operations rely on both synchronous and

asynchronous operations. Synchronous operations

means that certain events happen at regularly timed

intervals. An example of this is the computer’s master

clink. Asynchronous means that the completion of one

event triggers the next event. An example of this is the

execution of instructions located sequentially in

memory. After an instruction is executed, the next

instruction cannot be executed until the program

counter has been incremented to fetch it. Timing gets

the computer going.

Timing circuits are used

throughout the computer, as you will see when we

discuss each of the functional areas.

Not all computers rely on a sophisticated timing

system. Some timing systems are very simplistic and

rely only on the computer’s master clock and one or two

other timing signals derived from the master clock to

start and stop events.

Still other more sophisticated

computers rely on the master clock and timing circuits

in each of the functional areas to start and stop

operations.

Some of the more common timing circuits you will

encounter include the following:

Master clock

Main timing chain

Main timing signals

Timing sequences

Sequence enables and control

Real-time clock

Monitor clock

Programmable interval timers

Arithmetic timing

5-3