(fig. 5-6), a variety of interrupt conditions, task or

executive state status, and hardware status (memory

lockout, hardware faults, and so forth). These registers

are often used with instructions where branching

conditions are used to change the sequence of

instruction execution.

The status indicating registers’ contents can be

sensed, loaded with new data bits, or stored into

memory by machine instruction. Many machine

instructions, particularly branching instructions, are

designed to sense the condition of specified register bits

to determine how the instruction itself is to be executed.

Other instructions are designed to modify the contents

of the register(s) to change state (executive or task) or

to enable/disable classes of interrupts; this is

accomplished by indexing. The contents of the status

indicating register(s) is/are normally stored into

memory as part of the interrupt processing operation.

Instruction and Control Operations

The control portion of the CPU for computers is

responsible for fetching, translating, and executing all

instructions (fig. 5-7). The CPU calls up or reads the

instructions one at a time either from consecutive

addresses or as dictated by the program from main

memory or read-only memory (ROM). The general

process of execution of a machine instruction can be

divided into four major parts: fetch (read) the

instruction, update the program counter or equivalent,

translate the instruction, and execute the instruction

specified by the function or op code.

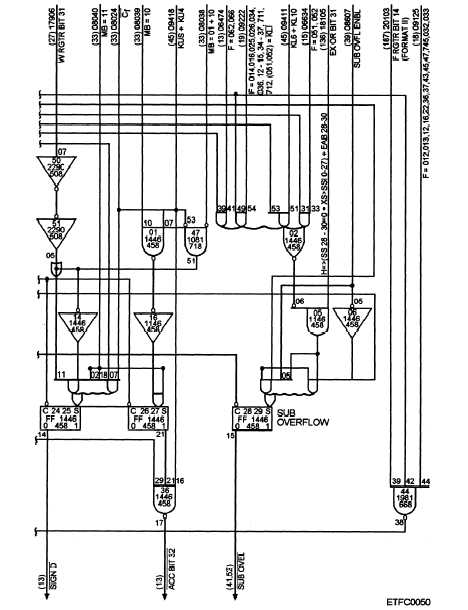

Figure 5-6.—Example of an arithmetic detecting circuit used to indicate a subtraction overflow condition.

5-8