read data from memory (output) or write data into

memory (input). The CPU still provides overall

control of the I/O operations, but it is not directly

involved in the actual data transfers between memory

and the external equipments. When the I/O section is

capable of memory access, the CPU provides I/O

commands to an I/O controller (IOC) or processor

and then goes about processing other necessary

operations. The IOC in turn controls all I/O operations

and interrupts the CPU operation when necessary to

inform it of event completion or problems with an I/O

interface channel or external device.

With this method, the CPU concentrates on its

essential business of processing information. We use

the keyboard again as our example. The keyboard is

ready to input characters. The keyboard interface

signals the CPU when a valid character is available in

its INBUF buffer. The CPU is performing some

computational task, when the keyboard sends an

interrupt request that generates an interrupt in the CPU.

When the interrupt request arrives, the CPU leaves its

current task, but not before making arrangements to

save all the data from computations just previous to the

interruption. The CPU leaves its current task and

executes the appropriate service routine. In this case it

receives the input from the keyboard interface and

promptly sends it to the desired location in the

computer. When the information has been routed to its

desired location and the input operation has been

completed, the CPU returns to its previous task.

Review chapter 5 of this volume for a detailed

discussion of the interrupt process.

An interrupt request can occur at any time. To

avoid confusion, most computers use a priority system

for requests in the event that two or more interrupts

arrive simultaneously. Interrupt driven I/Os use a

priority system to honor requests and interrupts. The

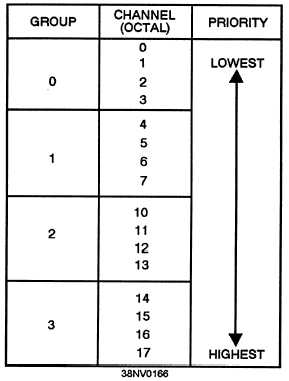

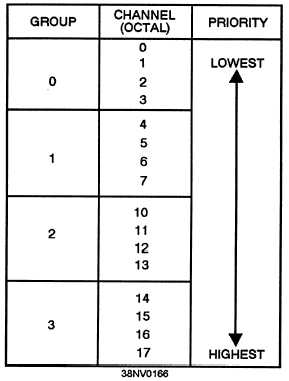

priority system is divided into channel and function

priorities. The channel priority performs priority

determination of requests and interrupts based on the

channel number. Figure 7-14 reflects channel priority

of a computer with 16 channels. Notice how they are

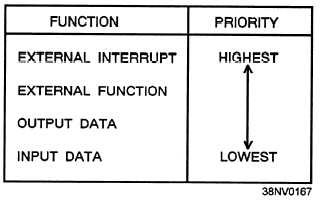

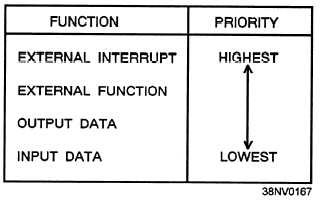

grouped and prioritized. Function priority determines

the order of honoring requests and interrupts when

channel priority honors more than one request per

channel. See figure 7-15.

Figure 7-14.—Channel priority determination.

Depending on the type of computer, interrupts are

categorized and the program can be written to meet

specific requirements when an interrupt occurs. Some

interrupt requests cannot be ignored. For example,

when a power failure interrupt occurs, the computer is

given the needed time to save information before the

computer system shuts down.

Direct Memory Access (DMA)

When the CPU is directly involved in each of the

I/O data transfers, it slows down the process of moving

information in and out of the computer. The use of

Figure 7-15.—Function priority determination.

7-16