Each I/O channel is assigned four memory

addresses in main memory or in logic circuitry

(registers) that replaces or overlays four

sequential main memory addresses. These four

addresses or registers are used to store the

following data:

address n

— External Interrupt Code Word

address n + 1 — Input Data Word

address n + 2 — Output Data Word

address n + 3 — Channel Control/Status Word

These addresses also allow the IOC/CPU

to perform interrupt driven or polled I/O

operations. Addresses n + 1 and n + 2 can be

used as single word buffers for polled

operations with the channel status word (n+ 3)

acting as the status word for the CPU to

periodically sample (poll).

POLLED I/O. —In polled I/O the CPU must

regularly check—or poll —each channel or port in turn

to determine if it has information for input or is ready

to accept data for output. A flag register can be used to

check the port’s status. Polling is time consuming. The

CPU must pause between executing processing

instructions and poll of each port. A port’s status is

examined in case action is required by the computer.

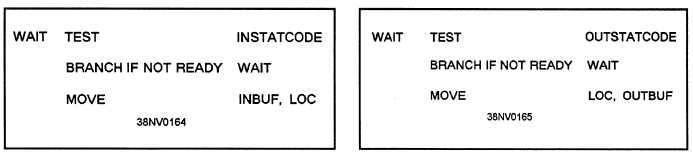

We use a keyboard as an example of polled I/O. Figure

7-12 shows a read operation. The CPU reads or

receives 8-bit encoded characters as they are typed on

the keyboard. The CPU is programmed to read the

input characters from an external device, in this case a

keyboard. The keyboard inputs parallel 8-bit character

codes for each depression of the keys. Characters are

entered slowly as compared to the CPU’s ability to

Figure 7-12.—Polled I/O; read operation.

process them. The dedicated CPU has to wait until the

next character is entered each time.

The CPU is programmed with what is known as an

I/O wait loop.

As the CPU executes the loop

instructions, it periodically (say 20 times a second)

checks the status code from the keyboard to see if a

character has been entered. A data register, INBUF, in

the keyboard interface receives the character data from

the keyboard. It holds the data until read by the CPU.

A status register, INSTATCODE, indicates whether

there is a new character in the INBUF register. By

continuously testing the status register, the CPU detects

when the code for a data entry is present. The CPU then

executes the instructions to transfer the data from the

data register to the specified location in the computer.

Once this has completed, the CPU returns to the wait

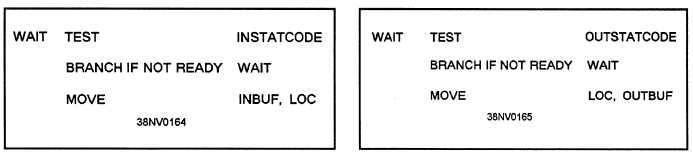

loop and polling process. The same procedure can be

used for output or write operations. Figure 7-13 shows

an output operation. In this case, the data is moved from

a computer location to the data output buffer of the

output device.

One of the disadvantages with polled I/O is that it

involves the CPU throughout the input/output process.

This is wasteful of CPU time. The CPU spends time

executing input/output instructions that it could be

spending performing other operations. Direct CPU

interface has its place, particularly in small computers

that are not concerned with high-speed operations and

processing very large amounts of data. Most of the

larger computers, however, use interrupt driven I/O.

INTERRUPT DRIVEN I/O. —The interrupt

technique requires more complex hardware and

software, but makes far more efficient use of the

computer’s time and capacities. In an interrupt driven

I/O the I/O section itself is capable of accessing

memory via the computer communication buses. The

I/O processor can, while conducting I/O operations,

Figure 7-13.—Polled I/O; write operation.

7-15