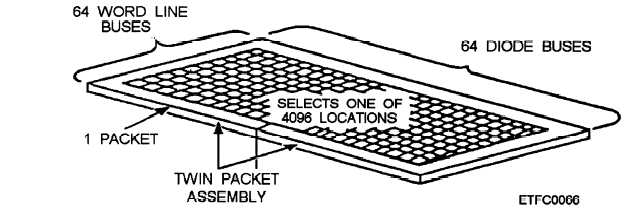

Figure 6-18.—Example portion of a film array.

FILM STORAGE LAYOUT. —Each paired thin

film can store one binary bit of data. But because of

their compactness, they have twice the storage capacity

in the same volume as core memory. Mated film

storage or film memory is designed to store a fixed

number of memory words. Mated film memory is

word organized. Each word line in a word organized

memory is selected by a unique memory address. The

film spots along a given word line are all the bits of a

particular word. When a current is propagated through

a selected word line, all the thin film spots along that

line are read in a simultaneous parallel manner, each

having a unique sense/digit line. Just like core memory,

the size of film storage or its memory capacity is

determined by the number of memory words that can

be used or addressed to store and retrieve data. To

accommodate a memory capacity of any size, the

memory words are organized into matrices.

Matrices. —The mated film spots are organized

into matrices called film arrays to simplify addressing,

reading, and writing operations. Figure 6-18 is an

example portion of a film array. Each film spot in the

film array has a word line pair and a sense/digit line;

they affect the read/write operations. Mated film

memories, like core memory, use a matrix.

Arrays. —In our example, a 64 by 64 array

contains 64 word line buses and 64 diode buses. They

select the exact word at a memory address location. By

selecting one word line and one diode, one of the 4096

(64 × 64 = 4096) memory locations in the array will be

selected. One 64 by 64 array forms two packets of a

memory stack.

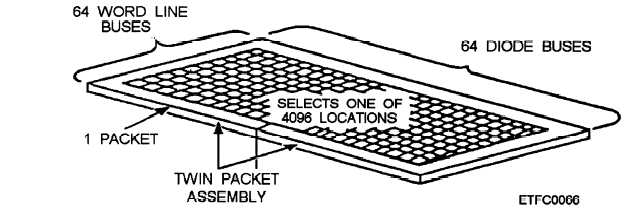

Memory Stack. —In mated film memory, the

packet is the building block of the film memory stack.

The mated film memory stack contains all the film spots

of the device, the associated circuitry that includes the

word lines, sense/digit lines, and associated hardware.

The associated hardware includes diode stick

assemblies and boards (diverter, insulators, and ground

planes, and alignment). Refer to figure 6-19 as an

illustration of a memory stack.

Figure 6-19.—Illustration of a memory stack.

6-16